Data Sheet August 11, 2009 FN4824.2

## Radiation Hardened 8 Channel CMOS Analog Multiplexer with Overvoltage Protection

The HS-508BRH is a dielectrically isolated, radiation hardened, CMOS analog multiplexer incorporating an important feature; it withstands analog input voltages much greater than the supplies. This is essential in any system where the analog inputs originate outside the equipment. They can withstand a continuous input up to 10V greater than either supply, which eliminates the possibility of damage when supplies are off, but input signals are present. Equally important, it can withstand brief input transient spikes of several hundred volts; which otherwise would require complex external protection networks. Necessarily, ON resistance is somewhat higher than similar unprotected devices, but very low leakage current combine to produce low errors. Reference Application Notes 520 and 521 for further information on the HS-508BRH multiplexer in general.

The HS-508BRH has been specifically designed to meet exposure to radiation environments. Operation from -55°C to +125°C is guaranteed.

#### **Features**

- Electrically Screened to SMD # 5962-96742

- QML Qualified per MIL-PRF-38535 Requirements

- Radiation Environment

- Gamma Dose (γ) . . . . . . . . . . . 3 x 10<sup>5</sup> Rad (Si)

- Dielectrically Isolated Device Islands

- SEP >100 Mev-mg/cm<sup>2</sup>

- Analog/Digital Overvoltage Protection

- ESD Rated to 3kV

- Fail Safe with Power Loss (No Latchup)

- · Break-Before-Make Switching

- (Typ) DTL/TTL and CMOS Compatible Threshold

- Analog Signal Range.....±15V

- Fast Access Time

- Supply Current at 1MHz Address Toggle . . . . . 4mA (Typ)

- Pb-Free (RoHS Compliant)

Specifications for Rad Hard QML devices are controlled by the Defense Supply Center in Columbus (DSCC). The SMD numbers listed here must be used when ordering.

Detailed Electrical Specifications for these devices are contained in SMD 5962-96742. A "hot-link" is provided on our homepage for downloading.

www.intersil.com/spacedefense/newsafclasst.asp

## **Ordering Information**

| ORDERING NUMBER (Note) | INTERNAL<br>MKT. NUMBER | PART MARKING       | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG. DWG. |

|------------------------|-------------------------|--------------------|---------------------|----------------------|-----------|

| 5962F9674202QEC        | HS1-508BRH-8            | Q 5962F96 74202QEC | -55 to +125         | 16 Ld SBDIP          | D16.3     |

| 5962F9674202QXC        | HS9-508BRH-8            | Q 5962F96 74202QXC | -55 to +125         | 16 Ld FLATPACK       | K16.A     |

| 5962F9674202VEC        | HS1-508BRH-Q            | Q 5962F96 74202VEC | -55 to +125         | 16 Ld SBDIP          | D16.3     |

| 5962F9674202VXC        | HS9-508BRH-Q            | Q 5962F96 74202VXC | -55 to +125         | 16 Ld FLATPACK       | K16.A     |

| HS1-508BRH/PROTO       | HS1-508BRH/PROTO        | HS1- 508BRH /PROTO | -55 to +125         | 16 Ld SBDIP          | D16.3     |

| HS9-508BRH/PROTO       | HS9-508BRH/PROTO        | HS9- 508BRH /PROTO | -55 to +125         | 16 Ld FLATPACK       | K16.A     |

NOTE: These Intersil Pb-free Hermetic packaged products employ 100% Au plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

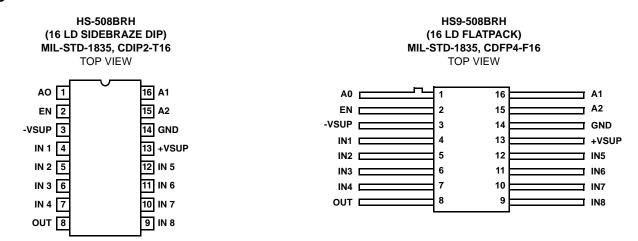

## **Pinouts**

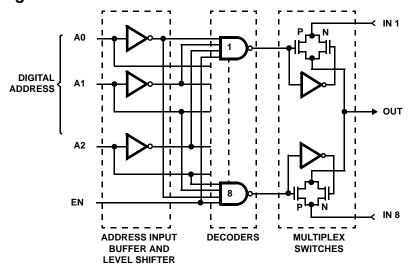

# Functional Diagram

**TABLE 1. TRUTH TABLE**

| A2 | A1 | A0 | EN | "ON" CHANNEL |

|----|----|----|----|--------------|

| Х  | Х  | Х  | L  | NONE         |

| L  | L  | L  | Н  | 1            |

| L  | L  | Н  | Н  | 2            |

| L  | Н  | L  | Н  | 3            |

| L  | Н  | Н  | Н  | 4            |

| Н  | L  | L  | Н  | 5            |

| Н  | L  | Н  | Н  | 6            |

| Н  | Н  | L  | Н  | 7            |

| Н  | Н  | Н  | Н  | 8            |

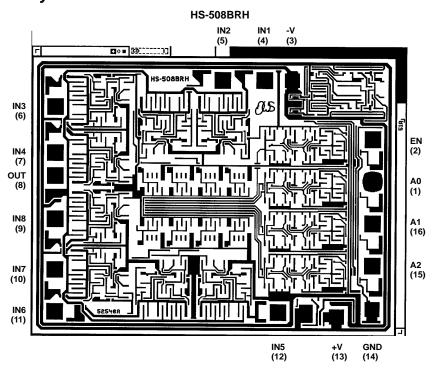

### Die Characteristics

**DIE DIMENSIONS**

120 mils x 93 mils x 19 mils

### **INTERFACE MATERIALS**

Glassivation

Type: Phosphorus Silicon Glass (PSG)

Thickness: 8kÅ ±1kÅ

**Top Metallization**

Type: AlSiCu

Thickness: 16kÅ ±2kÅ

**Substrate**

Rad Hard Silicon Gate Dielectric Isolation

**Backside Finish**

Silicon

**ASSEMBLY RELATED INFORMATION**

**Substrate Potential**

Unbiased (DI)

**ADDITIONAL INFORMATION**

**Worst Case Current Density**

6.68e04 A/cm<sup>2</sup>

**Transistor Count**

506

# Metallization Mask Layout

**TABLE 2. HS-508BRH PAD COORDINATES**

|            |          | RELATIVE TO PIN 1 |               |  |

|------------|----------|-------------------|---------------|--|

| PIN NUMBER | PAD NAME | X COORDINATES     | Y COORDINATES |  |

| 1          | A0       | 0                 | 0             |  |

| 2          | EN       | -342              | 0             |  |

| 3          | V-       | -818              | -653          |  |

| 4          | IN1      | -818              | -879          |  |

| 5          | IN2      | -818              | -1221         |  |

| 6          | IN3      | -598              | -2579         |  |

| 7          | IN4      | -224              | -2579         |  |

| 8          | OUT      | -38               | -2579         |  |

### HS-508BRH

TABLE 2. HS-508BRH PAD COORDINATES (Continued)

|            |          | RELATIVE TO PIN 1 |               |  |  |

|------------|----------|-------------------|---------------|--|--|

| PIN NUMBER | PAD NAME | X COORDINATES     | Y COORDINATES |  |  |

| 9          | IN8      | 314               | -2579         |  |  |

| 10         | IN7      | 724               | -2579         |  |  |

| 11         | IN6      | 1066              | -2579         |  |  |

| 12         | -IN5     | 1066              | -761          |  |  |

| 13         | V+       | 1100              | -287          |  |  |

| 14         | GND      | 1038              | 0             |  |  |

| 15         | A2       | 684               | 0             |  |  |

| 16         | A1       | 342               | 0             |  |  |

|            |          |                   |               |  |  |

NOTE: Dimensions in microns

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com